Family name: ...... Group: ...... Group: ...... **ANSWER SHEET** Exercise 1 2. 1. Q1 Q0  $\mathbf{Q}\mathbf{2}$  $\mathbf{Q0}$  $\mathbf{D2}$ **D1**  $\mathbf{D0}$ Q1  $\mathbf{D0}$ 00 01 11 **10** 1 1 1 0 1 0 1  $\mathbf{Q}\mathbf{2}$ 1 0 0 1 0 1 1 D0 =0 1 0 0 0 1 0 0 0 Q1 Q0 Q1 Q0 **D1** 00 01  $\mathbf{D2}$ 00 01 11 **10** 11 **10** Q2  $\mathbf{Q}\mathbf{2}$ 1 1 **D1** = **D**2 = Exercise 2 1. ROM: 2. Device-selection bits: RAM: P1: P2:  $CS_{P1} =$ 3.  $CS_{ROM} =$  $CS_{P2} =$  $CS_{RAM} =$ 4. **Lowest Address Highest Address Device ROM** RAM P1

Final Exam S2 3/5

P2

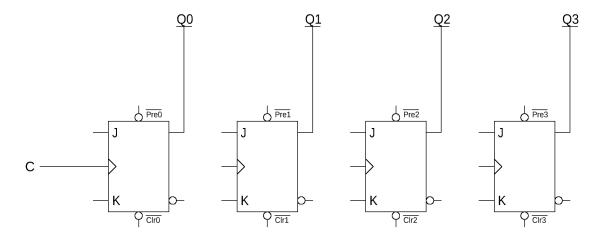

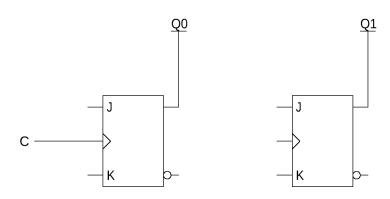

## Exercise 3

Figure 1

Figure 2

## Exercise 4

1.

| Number    | S | E | M |

|-----------|---|---|---|

| 428       |   |   |   |

| 51.078125 |   |   |   |

2.

| IEEE-754 Representation | Associated Representation |

|-------------------------|---------------------------|

| 435400000000000016      |                           |

| 001010000000000016      |                           |

Final Exam S2 4/5

## Exercise 5

| Question about memory devices                                                                                                                                                                                 | Answer |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| How can we connect memory devices in order to enlarge the depth?                                                                                                                                              |        |

| A memory has a width of 4 bits and a capacity of 64 KiB. How many address lines does this memory have?                                                                                                        |        |

| A memory has an 8-bit data bus and a 15-bit address bus. In a power of two, what is the capacity in bits of this memory?                                                                                      |        |

| An <b>M1</b> memory has an 8-bit data bus and a 16-bit address bus. Two <b>M1</b> memories are connected in series to build an <b>M2</b> memory. What is the size of the address bus of the <b>M2</b> memory? |        |

Final Exam S2 5/5